- 1. DSP system interference generation analysis

- 2. PCB design for the causes of Interference

- Conclusion

With the widespread use of DSP (Digital Signal Processor), developing high-speed signal-processing PCB boards based on DSP is particularly important. The DSP microprocessor operating frequency can be as high as hundreds of MHz in a DSP system. Its reset line, interrupt and control lines, integrated circuit switches, high-precision A/D conversion circuits, and circuits containing weak analogue signals are very susceptible to Interference, so the design and development of a stable and reliable DSP system and anti-interference design is very important.

Interference means that the interference energy puts the receiver in an undesired state. Interference is generated in two ways: direct (through conductors, common impedance coupling, Etc.) and indirect (through crosstalk or radiation coupling). Many electrical emission sources, such as light, motors and fluorescent lamps, can cause Interference, and electromagnetic Interference EMI can have an impact in three necessary ways, namely, the source of Interference, propagation paths and Interference receptors; only one of which needs to be cut off to solve the problem of electromagnetic Interference.

1. DSP system interference generation analysis

In order to make a stable and reliable DSP system, Interference must be eliminated from all aspects; even if it cannot be eliminated, it must be minimized. For DSP systems, the main Interference comes from the following areas.

① Input and output channel interference. Refers to Interference entering the system through the forward and backward channels, such as the data acquisition link of the DSP system, where Interference is iteratively added to the signal through the sensor, increasing the error of data acquisition. In the output link, the Interference can increase the error of the output data or even be completely wrong, causing the system to crash. Can reasonably use optocoupler devices to reduce the input and output channel interference, for sensors and DSP main system interference can use electrical isolation to Yang file thousand disturbance speak.

② Interference from the power supply system. The main source of Interference for the entire DSP system. The power supply in the system to provide power at the same time will also add noise to the power supply, which must be decoupled in the of the power line.

③ space radiation coupling interference. Crosstalk occurs when the electromagnetic field generates the current flow through the wire. The electromagnetic field in the adjacent wire induces transient currents, distorting the adjacent signal or even causing the error. The strength of crosstalk depends on the device, the geometry of the wires and the distance between them. In DSP wiring, the larger the signal line spacing and the closer to the ground, the more effective it is in reducing crosstalk.

2. PCB design for the causes of Interference

The following gives how to reduce various Interference in making the PCB of DSP systems.

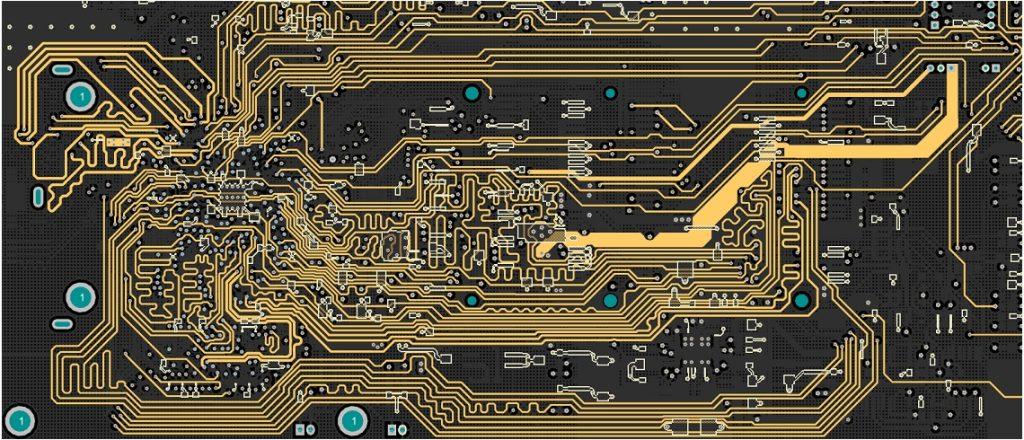

2.1 Multi-layer board laminated design

In order to improve signal quality, reduce the difficulty of wiring and increase the EMC of the system, the general use of multi-layer board laminated design is DSP high-speed digital circuits. The laminated design can provide the shortest return path, reduce the coupling area, and suppress differential mode interference. In the laminated design, dedicated power and ground layers are allocated, and the ground and power layers are tightly coupled to benefit common mode interference suppression (using adjacent planes to reduce the power plane AC impedance).

There are many advantages to using this 4-layer PCB design structure. In the top layer (top layer) below a power layer, the power pins of components can be directly connected to the power supply without crossing the ground plane. Critical signal selection in the bottom layer (bottom layer) so that the important signal alignment space is larger and the device is as much as possible on the same level. If not necessary, do not do 2 layers of parts of the board, increasing the assembly time and complexity, such as a top layer, only when the top layer components are too dense, only the height of the limited and low heat generation devices, like decoupling capacitors (SMD) in the bottom layer. A cascading design allows the wires to be routed on the inner layer for DSP systems that may have many wires to be laid. If you follow the traditional through-hole will waste a lot of valuable alignment space, you can use the blind / buried via (blind / buried via) to increase the alignment area.

2.2 Layout design

In order to get the best performance of the DSP system, the layout of the components is very important. First, place the DSP, Flash, SRAM and CPLD devices, which carefully consider the alignment space, then place other ICs according to the principle of functional independence, and finally consider the placement of I/O ports. Combine the above layout and then consider the size of the PCB: if the size is too large, it will make the printed lines too long, impedance increases, noise resistance decreases, and the cost of board making will also increase; if the PCB is too small, it is not good for heat dissipation, and limited space, the neighbouring lines are susceptible to Interference. Therefore, the actual need to select the device, combined with the alignment space, and the size of the PCB, is largely calculated. In the layout of the DSP system, the placement of the following devices is paid special attention.

(1) High-speed signal layout

The DSP and Flash SRAM is the main high-speed digital signal lines in the entire DSP system, so the distance between the devices should be as close as possible, their connection lines as short as possible, and directly connected. Therefore, to reduce the impact of transmission lines on signal quality, the high-speed signal alignment should be as short as possible. Consider also that many DSP chips with speeds of several hundred MHz require snake winding (delay tune). It will be highlighted in the following wiring.

(2) Layout of digital and analogue devices

Most DSP system is not single functional circuit. Many CM0S digital devices and digital-analogue hybrid devices are used, so the layout of digital/analogue should be separated. Analog signal devices are concentrated as much as possible so that the analogue ground can be drawn in the middle of the entire digital ground, an independent area belonging to the analogue signal, to avoid Interference from the digital signal to the analogue signal. Some mixed digital-analogue devices, such as D / A converters, traditionally regarded as analogue devices, put it on the analogue ground, and to provide a digital circuit, so that digital noise feedback back to the signal source, reducing the impact of digital noise on the analogue ground.

(3) Layout of the clock

The clock, chip select and bus signals should be as far away as possible from the I/O lines and connectors. The clock input of the DSP system, which is susceptible to Interference, is very critical to its handling. Always ensure that the clock generator is as close to the DSP chip as possible so that the clock lines are as short as possible. The case of the clock crystal oscillator is best grounded.

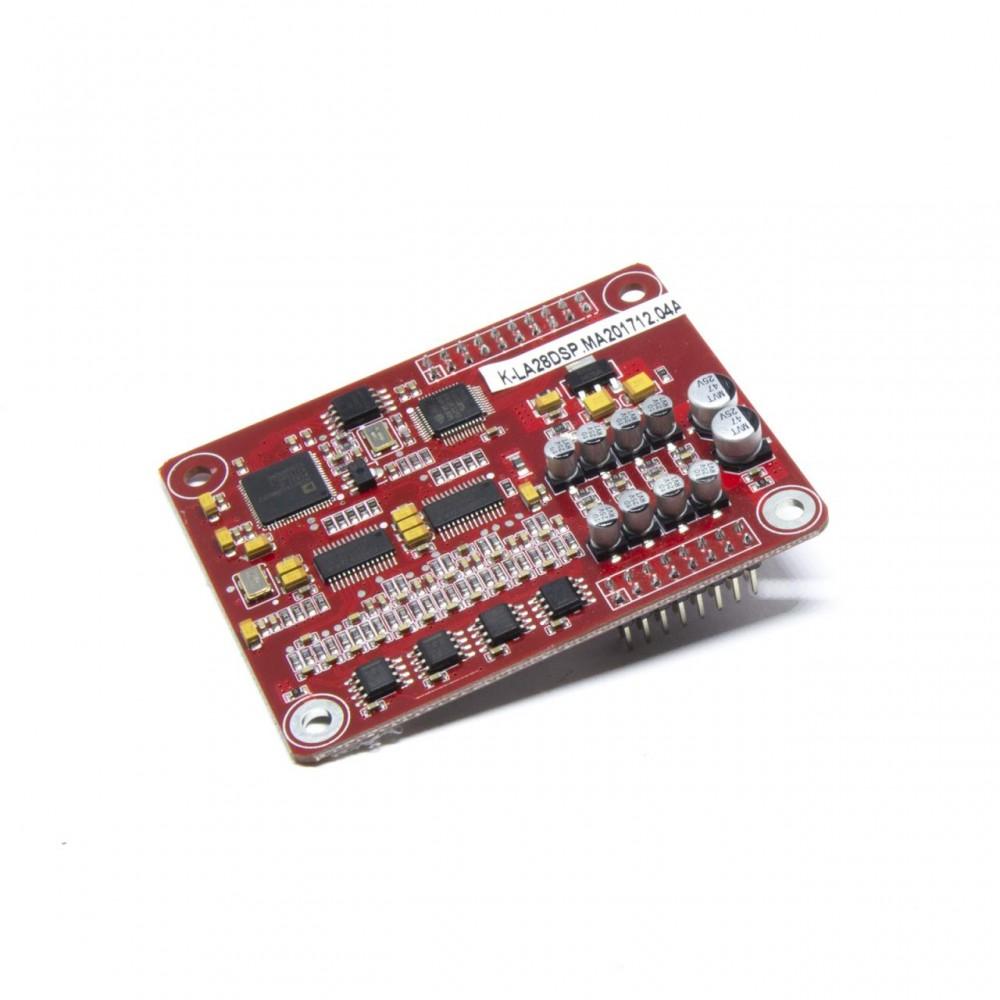

(4) Decoupling layout

To reduce the transient voltage overshoot on the IC chip power supply, add decoupling capacitors to the IC chip, which can effectively remove the impact of burrs on the power supply and reduce the power loop reflection on the PCB. Adding decoupling capacitors can bypass the IC device’s high-frequency noise and act as energy storage capacitors to provide and absorb the quick charge and discharge energy of the IC switching gate.

In DSP systems, decoupling capacitors are placed for each IC, like DSP, SRAM, Flash, Etc., added between each power supply and ground of the chip. Special attention should be paid to the decoupling capacitors as close as possible to the power supply side (source) and the IC’s part pin (pin). Ensure the purity of the current from the power supply side (source side) into the IC, and try to make the noise path as short as possible. When dealing with capacitors, use large vias or multiple vias. The line between vias to capacitors should be as short and thick as possible. 2 vias are not good when they are far away because the path is too large; the best is to decouple the 2 vias of the capacitor as closely as possible, which can make the noise to ground with the shortest path.

Also, it is very advantageous to add a high-frequency capacitor at the power input or battery supply. The value of the decoupling capacitor is not very strict, generally calculated by C = l /, that is, the frequency of 10 MHz to take 0.1μF capacitance.

(5) The layout of the power supply

The power supply needs to be carefully considered in developing the DSP system. Because some power supply chips generate heat, they should be prioritized in a location conducive to heat dissipation to be separated from other components at a certain distance. Heat dissipation can be done by adding a heat sink or laying copper under the device. Be careful not to place heat-generating components on the bottom of the development board.

(6) Other notes

The layout of other DSP system components should take into account the requirements of easy soldering, easy debugging and aesthetics. As potentiometers, adjustable inductor coils, variable capacitors, dip switches, and other adjustable devices should be placed in conjunction with the overall structure. For more than 15 g devices to add fixed brackets and then welding, with special attention to the PCB positioning holes and fixed brackets occupied by the location of the PCB edge of the components from the PCB edge distance is generally not less than 2 mm, the PCB is best rectangular, the length to width ratio of 3:2 or 4;3.

2.3 Wiring design

After carefully considering increasing the DSP system’s anti-interference and enhancing EMC’s layout capability, the wiring should also have some measures and techniques.

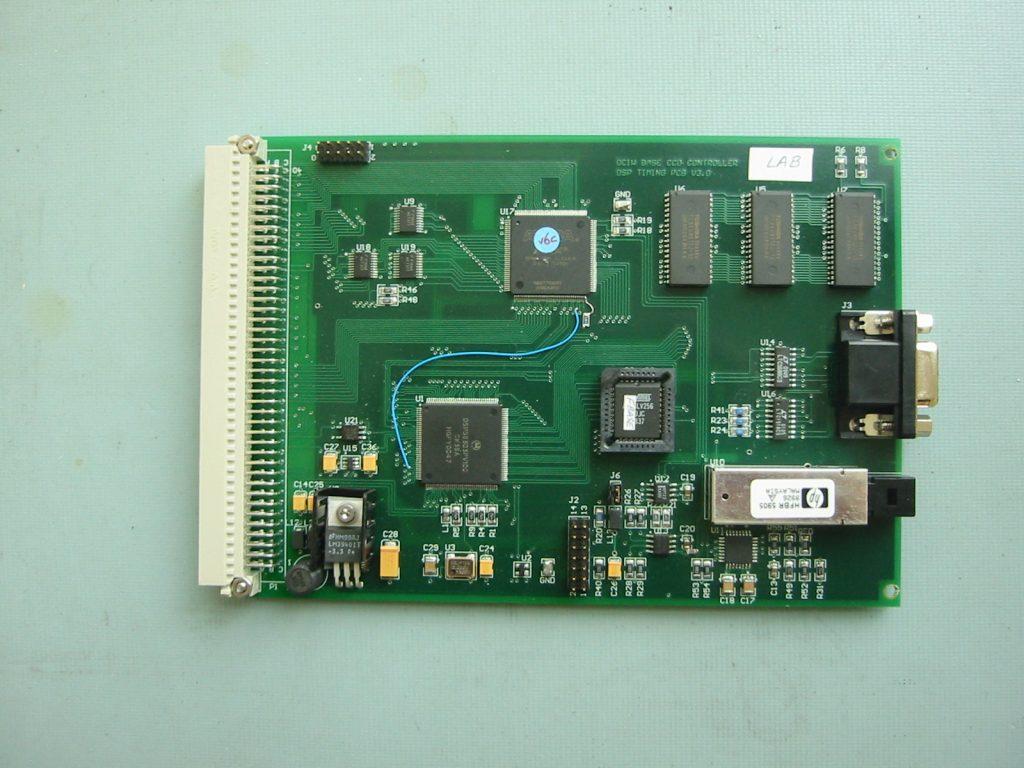

(1) Wiring of DSP

The wiring is largely started from the core device and unfolded with it as the centre. For devices such as DSP in PQFP (Plastic Quad FIat Pack) or BGA (BaIl Grid Array) packages, you should first determine the general direction of the alignment based on the layout position of SRAM, Flash and CPLD and fan out (fanout) operation for the pins. Especially for QFP & BGA type devices, fanout is especially important. Fun outing the pins of BGA-type devices at the beginning of wiring can save time for later wiring and improve the quality and efficiency of wiring. When wiring, the features of EDA tools, such as dynamic routing of power PCB, can be used to plan the space optimally. When using dynamic, this feature will automatically keep the space between lines inside the rules so as not to waste space, reduce subsequent modifications, and improve the quality and efficiency of wiring.

For high-speed DSP, attention should also be paid to crosstalk and snake line (delay tune) line processing. Snake line processing can ensure the integrity of the signal and the continuity of the high-speed signal reference plane. In the need for plane division, be sure to pay attention not to let the high-speed line across the discontinuous plane; it must cross and add capacitance across the plane.

When the signal line (trace) interval is 3 times the width of the signal line, the chance of mutual crosstalk between signals (coupling) is only about 25% so that you can achieve the requirements of anti-electromagnetic Interference (EMI). Therefore, like CLK and SRAM these high-speed signal lines, remember to stay away from it next to the signal line more than 3 times the width, the transfer of equal length, that is, the snake alignment, line and line width should also be more than 3 times the width of the signal line, including for its signal line should also be 3 times the width of the signal line. The line width is 5 mil*, and the distance inside the winding itself is 15 mil, greater than or equal to 3 times the line width.

(2)Clock wiring

For the clock signal, make its alignment distance for other signals as large as possible to ensure that the distance is 4 times the line width or more and does not go under the clock (parts); for the analogue voltage input line, the reference voltage terminal and I / 0 signal line as far away from the clock.

(3) The handling of the system power supply

The power supply is the most important part of the system. A separate power supply layer is allocated in the laminated design of the PCB. However, because a DSP system has a variety of digital and analogue devices, the power is used by a variety of power supplies, so the power supply layer is divided so that the same power characteristics of the device are divided in the same area, can be connected to the power supply layer nearby. However, special attention should be paid to partitioning so that the signal in the reference power plane is continuous. After experimental proof, the 40 mil line width, can pass the current and can be guaranteed to have 1A; for over the aperture diameter of 16 mils can pass 1 A current, so for the DSP system, the power line is greater than 20 mils can be. The line should pay attention to the following points for electromagnetic radiation protection on the power.

◆ Limiting the leakage of AC on the board with bypass capacitors.

◆ Connect a common mode choke (common mode choke) in series on the power line to suppress the common mode current flowing through the line.

◆ Wiring close together to reduce the magnetic radiation area.

(4) Handling of grounding

In all EMC problems, the main problem is caused by improper grounding. The good or bad grounding treatment directly affects the stability and reliability of the system. Grounding has the following functions.

◇Reducing the common mode voltage VCM on the output line.

◇Reducing the sensitivity to static electricity (ESD).

◇Reducing electromagnetic radiation.

The ground loops of high-frequency digital circuits and low-frequency analogue circuits should never be mixed, and the digital circuits and analogue signal circuits must be separated because digital circuits generate noise in the power supply and ground when switching between high and low potentials; if the ground plane is not separated, the analogue signals will still be interfered by ground noise. So the high-frequency signal should be multi-point series grounding, as thick as possible, to shorten the ground, reduce the voltage drop, and reduce coupling noise. However, for a system, no matter how to divide, the final earth is only one, just a different lagging path, so finally, through the magnetic beads or 0 n resistance, the digital ground and analogue ground are connected to eliminate mixed signal interference.

When the ground plane is divided, the continuity of the reference plane must be ensured. Like digital circuits and analogue signals, circuits coexist. If the analogue signal lines go farther away, the PCB board should try to make its reference return path also analogue ground. In the ground layer, cut an analogue ground along the path of the analogue signal so that its reference analogue ground ensures the continuity of its reference plane.

(5) Other precautions

(1) In wiring, the corners of the wires generally do not go into a 90° fold to reduce the external emission coupling of high-frequency signals.

② When laying copper on the PCB, try to avoid the use of large-area copper foil, otherwise after a long period of heat, easy to occur the phenomenon of copper foil off; must use a large area of copper foil can be replaced by a grid, which is conducive to the exclusion of copper foil and the substrate between the adhesive heat generates volatile gas. In the penetration of the parts on foot (DIPPIN) lay, the copper foil is also best to use the thermal pad (thermal) processing; it should avoid false soldering and improve the yield.

③ The input and output edge lines should avoid adjacent parallel to avoid reflection interference; add ground isolation if necessary. The wiring of two adjacent layers should be perpendicular to each other; parallel is easy to produce coupling.

④For I / 0, it is best to be able to split the different areas of the respective reference planes so that different I/O signals do not interfere with each other.

Conclusion

This paper first analyzes the Interference to the DSP system to determine the main causes of possible Interference. It then minimizes the possible Interference to the DSP system from various aspects by using the laminated design of the PCB board, device layout and detailed wiring methods for various causes. The various interference reduction methods in the paper have been applied to developing an existing DSP system (TI’s DSP chip TMS320LF2407) with good results.